億金技術(shù)支持:Oscillator輸出類(lèi)型指南

來(lái)源:http://m.sanctuaryinlakeelmo.com 作者:億金電子 2020年07月14

Oscillator輸出類(lèi)型是關(guān)于振蕩器的常見(jiàn)問(wèn)題,有源晶振的輸出類(lèi)型又分為正玄波輸出和方波輸出,還可分為單端輸出和差分輸出,而單端輸出和差分輸出又可向下繼續(xù)細(xì)分;那么這些輸出類(lèi)型之間到底是有什么聯(lián)系和區(qū)別呢?客戶在選型的時(shí)候根據(jù)應(yīng)用和所需的操作頻率怎么樣才能找到最適合產(chǎn)品的輸出類(lèi)型的?

如上問(wèn)所述,振蕩器的輸出類(lèi)型分為兩大類(lèi)型,一是方波,輸出頻率波形呈現(xiàn)矩形波的樣式,而是正玄波,輸出頻率信號(hào)呈現(xiàn)三腳正玄波的形狀.

正玄波如下圖所示,它創(chuàng)建了一個(gè)連續(xù)的模擬正弦波,用頻率和幅度的掃描周期表示. 方波–如下圖所示,是振蕩器輸出的數(shù)字表示.其信號(hào)以頻率和幅度的速率由90度周期表示

.jpg) 單端輸出分為如下幾種:

單端輸出分為如下幾種:

1)正弦波和削波正弦波

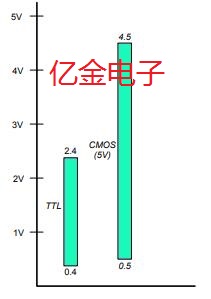

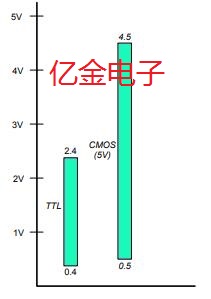

2)TTL(晶體管到晶體管邏輯)0.4?2.4V

3)CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)0.5?4.5V

4)HCMOS(高速CMOS)0.5?4.5V

5)LVCMOS(低壓CMOS)0.5?4.5V

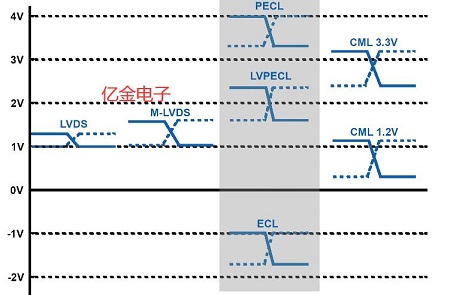

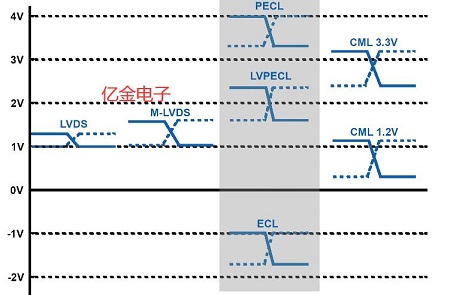

差分輸出又分為下列這幾種:

1)PECL(正發(fā)射極耦合邏輯)3.3?4.0V

2)LVPECL(低壓PECL)1.7?2.4V

3)CML(電流模式邏輯)0.4?1.2V和2.6?3.3V

4)LVDS(低壓差分信號(hào))1.0?1.4V

5)HCSL(高速電流轉(zhuǎn)向邏輯)0.0?0.75V

雖然將單端輸出和差分輸出列舉出來(lái)了,也介紹了有哪些輸出方式,但是還沒(méi)說(shuō)怎么樣去選擇最合適;選擇的話我們就要對(duì)每一種輸出方式的原理有一定了解,所以先來(lái)看看它們各自的優(yōu)缺點(diǎn).

正玄波和削頂正玄波:

正弦波是晶體或石英晶體振蕩器電路的標(biāo)準(zhǔn)或”自然”信號(hào)輸出.它由一個(gè)基本正弦頻率輸出組成.線性正弦波輸出可在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號(hào)的應(yīng)用.圖中紅色的即為正玄波.

削波正弦波正弦波輸出受到控制,因此不會(huì)達(dá)到其最大高電平或低電平.這樣,您將創(chuàng)建一個(gè)方波輸出,而不會(huì)犧牲任何所需的相位噪聲性能.圖中黃色的即為削頂正玄波.

.jpg) CMOS,HCMOS和LVCMOS

CMOS,HCMOS和LVCMOS

CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類(lèi)別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許時(shí)鐘輸出和芯片輸入之間的直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來(lái)有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能會(huì)更適合您的特定需求.

TTL或晶體管到晶體管邏輯

這是一個(gè)較舊的數(shù)字輸出標(biāo)準(zhǔn),已被CMOS技術(shù)取代.這是因?yàn)镃MOS提供了更低的成本和更好的噪聲性能.CMOS和TTL都非常適合低功耗,較高的輸出擺幅以及相對(duì)較低的成本.

而差分輸出信號(hào)提供雙相異相180°的輸出信號(hào)線.這對(duì)信號(hào)質(zhì)量有很多好處,比如可以更好的上升和下降時(shí)間,再比如具備出色的抖動(dòng)和相位噪聲性能,還可以改進(jìn)的共模噪聲抑制,還能夠幫助減少電磁和射頻干擾.

而差分輸出信號(hào)提供雙相異相180°的輸出信號(hào)線.這對(duì)信號(hào)質(zhì)量有很多好處,比如可以更好的上升和下降時(shí)間,再比如具備出色的抖動(dòng)和相位噪聲性能,還可以改進(jìn)的共模噪聲抑制,還能夠幫助減少電磁和射頻干擾.

ECL或發(fā)射極耦合邏輯

ECL主要是作為T(mén)TL的一種很好的替代方法引入的.ECL電路可以非常快速地改變狀態(tài),這使其更適合于高速數(shù)據(jù)傳輸.差分輸出的缺點(diǎn)之一是它們需要更高的電源電流才能工作.ECL在使用過(guò)程中還會(huì)使用負(fù)電源.嘗試連接到正極基礎(chǔ)電源設(shè)備時(shí),這可能會(huì)帶來(lái)挑戰(zhàn).

PECL和LVPECL

PECL輸出經(jīng)常在高速時(shí)鐘分配電路中使用.這是因?yàn)镻ECL具有很高的抗噪能力,能夠在較長(zhǎng)的線路長(zhǎng)度上驅(qū)動(dòng)高數(shù)據(jù)速率,并且由于電壓擺幅較大而具有良好的抖動(dòng)性能.但是,PECL需要高功耗才能運(yùn)行,這是主要缺點(diǎn).

LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但是提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會(huì)帶來(lái)挑戰(zhàn),因?yàn)樾枰私觼?lái)發(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查正確的端接以達(dá)到最佳性能.

電流模式邏輯(CML)

CML具有與LVPECL相似的性能.這里的主要區(qū)別是CML不需要外部偏置.當(dāng)需要考慮低功耗時(shí),這使得CML可以替代LVPECL.

低壓差分信號(hào)(LVDS)

LVDS類(lèi)似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.為了獲得更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,它們將需要更多的功耗.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).

LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

高速電流轉(zhuǎn)向邏輯(HCSL)

HCSL具有較新的輸出標(biāo)準(zhǔn),例如LVPECL.HCSL的優(yōu)點(diǎn)之一是其高阻抗輸出和快速切換時(shí)間.建議使用10至30歐姆的串聯(lián)電阻,以減少可能的過(guò)沖和振鈴.其他優(yōu)點(diǎn)包括最快的開(kāi)關(guān)速度,低功耗(介于LVDS和LVPECL之間)以及平均到良好的相位噪聲性能.

由此可見(jiàn),我們可以這樣選擇振蕩器想要的輸出方式;當(dāng)只為易于使用的時(shí)候就選擇我LVDS,該類(lèi)型在接收器處只需要一個(gè)電阻,而LVPECL在發(fā)送器和接收器上都需要端接;當(dāng)輸出頻率很高時(shí),選擇LVDS,LVPECL和HCSL比CMOS以達(dá)到更快速的過(guò)渡,但是需要的驅(qū)動(dòng)功率比較大,功耗也比較高;當(dāng)要求功耗較低時(shí)可選擇CMOS或LVDS(頻率低于150MHz);當(dāng)需要達(dá)到最佳抖動(dòng)性能的時(shí)候可LVPECL,LVDS和CMOS,當(dāng)然輸出頻率得足夠低.

由此可見(jiàn),我們可以這樣選擇振蕩器想要的輸出方式;當(dāng)只為易于使用的時(shí)候就選擇我LVDS,該類(lèi)型在接收器處只需要一個(gè)電阻,而LVPECL在發(fā)送器和接收器上都需要端接;當(dāng)輸出頻率很高時(shí),選擇LVDS,LVPECL和HCSL比CMOS以達(dá)到更快速的過(guò)渡,但是需要的驅(qū)動(dòng)功率比較大,功耗也比較高;當(dāng)要求功耗較低時(shí)可選擇CMOS或LVDS(頻率低于150MHz);當(dāng)需要達(dá)到最佳抖動(dòng)性能的時(shí)候可LVPECL,LVDS和CMOS,當(dāng)然輸出頻率得足夠低.

如上問(wèn)所述,振蕩器的輸出類(lèi)型分為兩大類(lèi)型,一是方波,輸出頻率波形呈現(xiàn)矩形波的樣式,而是正玄波,輸出頻率信號(hào)呈現(xiàn)三腳正玄波的形狀.

正玄波如下圖所示,它創(chuàng)建了一個(gè)連續(xù)的模擬正弦波,用頻率和幅度的掃描周期表示. 方波–如下圖所示,是振蕩器輸出的數(shù)字表示.其信號(hào)以頻率和幅度的速率由90度周期表示

.jpg)

1)正弦波和削波正弦波

2)TTL(晶體管到晶體管邏輯)0.4?2.4V

3)CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)0.5?4.5V

4)HCMOS(高速CMOS)0.5?4.5V

5)LVCMOS(低壓CMOS)0.5?4.5V

差分輸出又分為下列這幾種:

1)PECL(正發(fā)射極耦合邏輯)3.3?4.0V

2)LVPECL(低壓PECL)1.7?2.4V

3)CML(電流模式邏輯)0.4?1.2V和2.6?3.3V

4)LVDS(低壓差分信號(hào))1.0?1.4V

5)HCSL(高速電流轉(zhuǎn)向邏輯)0.0?0.75V

雖然將單端輸出和差分輸出列舉出來(lái)了,也介紹了有哪些輸出方式,但是還沒(méi)說(shuō)怎么樣去選擇最合適;選擇的話我們就要對(duì)每一種輸出方式的原理有一定了解,所以先來(lái)看看它們各自的優(yōu)缺點(diǎn).

正玄波和削頂正玄波:

正弦波是晶體或石英晶體振蕩器電路的標(biāo)準(zhǔn)或”自然”信號(hào)輸出.它由一個(gè)基本正弦頻率輸出組成.線性正弦波輸出可在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號(hào)的應(yīng)用.圖中紅色的即為正玄波.

削波正弦波正弦波輸出受到控制,因此不會(huì)達(dá)到其最大高電平或低電平.這樣,您將創(chuàng)建一個(gè)方波輸出,而不會(huì)犧牲任何所需的相位噪聲性能.圖中黃色的即為削頂正玄波.

.jpg)

CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類(lèi)別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許時(shí)鐘輸出和芯片輸入之間的直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來(lái)有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能會(huì)更適合您的特定需求.

TTL或晶體管到晶體管邏輯

這是一個(gè)較舊的數(shù)字輸出標(biāo)準(zhǔn),已被CMOS技術(shù)取代.這是因?yàn)镃MOS提供了更低的成本和更好的噪聲性能.CMOS和TTL都非常適合低功耗,較高的輸出擺幅以及相對(duì)較低的成本.

ECL或發(fā)射極耦合邏輯

ECL主要是作為T(mén)TL的一種很好的替代方法引入的.ECL電路可以非常快速地改變狀態(tài),這使其更適合于高速數(shù)據(jù)傳輸.差分輸出的缺點(diǎn)之一是它們需要更高的電源電流才能工作.ECL在使用過(guò)程中還會(huì)使用負(fù)電源.嘗試連接到正極基礎(chǔ)電源設(shè)備時(shí),這可能會(huì)帶來(lái)挑戰(zhàn).

PECL和LVPECL

PECL輸出經(jīng)常在高速時(shí)鐘分配電路中使用.這是因?yàn)镻ECL具有很高的抗噪能力,能夠在較長(zhǎng)的線路長(zhǎng)度上驅(qū)動(dòng)高數(shù)據(jù)速率,并且由于電壓擺幅較大而具有良好的抖動(dòng)性能.但是,PECL需要高功耗才能運(yùn)行,這是主要缺點(diǎn).

LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但是提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會(huì)帶來(lái)挑戰(zhàn),因?yàn)樾枰私觼?lái)發(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查正確的端接以達(dá)到最佳性能.

電流模式邏輯(CML)

CML具有與LVPECL相似的性能.這里的主要區(qū)別是CML不需要外部偏置.當(dāng)需要考慮低功耗時(shí),這使得CML可以替代LVPECL.

低壓差分信號(hào)(LVDS)

LVDS類(lèi)似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.為了獲得更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但與LVDS相比,它們將需要更多的功耗.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).

LVDS的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是正在尋求新技術(shù)以實(shí)現(xiàn)與LVPECL相同水平的抖動(dòng)性能.

高速電流轉(zhuǎn)向邏輯(HCSL)

HCSL具有較新的輸出標(biāo)準(zhǔn),例如LVPECL.HCSL的優(yōu)點(diǎn)之一是其高阻抗輸出和快速切換時(shí)間.建議使用10至30歐姆的串聯(lián)電阻,以減少可能的過(guò)沖和振鈴.其他優(yōu)點(diǎn)包括最快的開(kāi)關(guān)速度,低功耗(介于LVDS和LVPECL之間)以及平均到良好的相位噪聲性能.

正在載入評(píng)論數(shù)據(jù)...

相關(guān)資訊

- [2024-11-09]溫度補(bǔ)償晶體振蕩器 JT21LE,功耗極低...

- [2023-06-26]Rakon推出RakonXpress品牌的現(xiàn)成頻率...

- [2023-06-20]Cardinal晶振公司環(huán)境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH證明,CX532Z-A2B3C5...

- [2023-06-17]為什么選擇ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含數(shù)字溫度補(bǔ)償?shù)臅r(shí)鐘IC...

- [2020-12-04]TXC晶振車(chē)規(guī)級(jí)頻率組件最新產(chǎn)品應(yīng)用方...

- [2020-10-19]石英振蕩器系列六——產(chǎn)品未來(lái)應(yīng)用市...

.jpg)

銷(xiāo)售代表

銷(xiāo)售代表

.jpg)